一、三管MOS DRAM基本单元电路原理

如果需要读出数据,首先需要给T4加上一个预充电信号,然后VDD给读数据线充电,代表需要读出的数据是“1”,进行读出时,读选择线是高电平。此时,如果原来存储在电容里面的数据是“0”,则电容为低电平,不带电,那么T1并不会接通。因此此时存的数据是“0”,读出的数据却是“1”。//相反,如果存的数据是“1”,那么T1管就会接通,T1、T2导通接地,所以此时读数据线为低电平,读出的数据就是“0”,。这就是“读出与原存信息相反”,因此需要在读数据线输出端加一个与门。

如果需要写入数据,写选择线为高电平,T3管接通,写数据线若是高电平,就会给Cg充电,写入数据“1”,如果写数据线是低电平,则Cg会通过T3管放电,存入的数据是“0”。这就是“写入与输入信息相同”。

壹芯微科技专注于“二,三极管、MOS(场效应管)、桥堆”研发、生产与销售,20年行业经验,拥有先进全自动化双轨封装生产线、高速检测设备等,研发技术、芯片源自台湾,专业生产流程管理及工程团队,保障所生产每一批物料质量稳定和更长久的使用寿命,实现高度自动化生产,大幅降低人工成本,促进更好的性价比优势!选择壹芯微,还可为客户提供参数选型替代,送样测试,技术支持,售后服务等,如需了解更多详情或最新报价,欢迎咨询官网在线客服!

手机号/微信:13534146615

QQ:2881579535

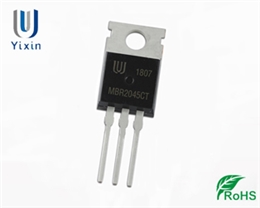

肖特基二极管MBR2045CT参数

肖特基二极管MBR2045CT参数 三极管S8050参数

三极管S8050参数 整流二极管SS34参数

整流二极管SS34参数 超快恢复二极管ES1JF参数

超快恢复二极管ES1JF参数