MOSFET击穿电压-MOS管击穿特性原因以及解决方案

MOSFET击穿电压有哪几种

场效应管的三极:源级(Source)S、漏级(Drain)D、栅级(Gate)G

(这里不讲栅极GOX击穿了啊,只针对MOSFET击穿电压漏极电压击穿)

先讲测试条件,都是源栅衬底都是接地,然后扫描漏极电压,直至Drain端电流达到1uA。所以从器件结构上看,它的漏电通道有三条:Drain(漏级)到source(源级)、Drain(漏级)到Bulk、Drain(漏级)到Gate(栅级)。

1)MOSFET击穿电压-Drain(漏极)->Source(源极)穿通击穿

这个主要是Drain(漏极)加反偏电压后,使得Drain(漏极)/Bulk的PN结耗尽区延展,当耗尽区碰到Source(源极)的时候,那源漏之间就不需要开启就形成了通路,所以叫做穿通(punchthrough)。那如何防止穿通呢,这就要回到二极管反偏特性了,耗尽区宽度除了与电压有关,还与两边的掺杂浓度有关,浓度越高可以抑制耗尽区宽度延展,所以flow里面有个防穿通注入(APT:AntiPunchThrough),记住它要打和well同type的specis。当然实际遇到WAT的BV跑了而且确定是从Source(源极)端走了,可能还要看是否PolyCD或Spacer宽度,或者LDD_IMP问题了,那如何排除呢这就要看你是否NMOS和PMOS都跑了POLYCD可以通过Poly相关的WAT来验证。

对于穿通击穿,有以下一些特征:

(1)穿通击穿的击穿点软,击穿过程中,电流有逐步增大的特征,这是因为耗尽层扩展较宽,产生电流较大。另一方面,耗尽层展宽大容易发生DIBL效应,使源衬底结正偏出现电流逐步增大的特征。

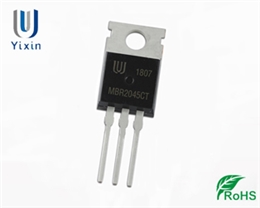

肖特基二极管MBR2045CT参数

肖特基二极管MBR2045CT参数 三极管S8050参数

三极管S8050参数 整流二极管SS34参数

整流二极管SS34参数 超快恢复二极管ES1JF参数

超快恢复二极管ES1JF参数