如图提问:

1. VDD_SN 的电压,这个电压肯定是要小于右边的 3.3V 的,因为什么呢?

VDD_SN 高于 3.3V,NMOS Q13 和 Q14 在关闭状态时,左边高于 3.3V 的电压就会通过 Q13 和 Q14 的体二极管到达 TP_SCL 和 TP_SDA 上,使其电压高于 3.3V,就有损坏单片机 IO 口的风险。

2. 这个电路的工作原理是什么呢?

SN2_SCL=0V,Q13 导通,TP_SCL=0;

SN2_SCL=1.8V,Q13 截止,TP_SCL=3.3V;能正常完成电平转换过程,SDA 信号是同样的道理。

3. 然后我又提到 MOS 管的开关时间,原因是什么呢?

左边到右边的数据传输,会有一个时间差,这个时间差一方面受到 NMOS 开关时间的影响,另一方面是总线容抗+上拉电阻(RC 时间常数)的影响。

假如 I2C 的速率是 400KHz,那传输 1bit 数据的时间就是 2.5us,如果 MOS 管的关闭时间参数大,加上 RC 较大,会出现如下比较差的上升沿波形,在这 2.5us 之内,1 位数据的传输可能无法满足时序要求,导致通信失败。

来自于嵌入式客栈

下降沿是单片机 IO 直接输出低电平,驱动能力比较足,所以时间差主要受 MOS 管开启时间影响。

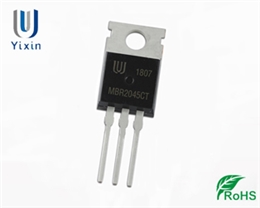

肖特基二极管MBR2045CT参数

肖特基二极管MBR2045CT参数 三极管S8050参数

三极管S8050参数 整流二极管SS34参数

整流二极管SS34参数 超快恢复二极管ES1JF参数

超快恢复二极管ES1JF参数